# SC4150 Negative Voltage Hot Swap Controller

## **POWER MANAGEMENT**

#### Description

The SC4150 is a negative voltage hotswap controller that allows the insertion of line cards into a live backplane.

The inrush current is programmable and closed loop operation limits the maximum current even under short circuit conditions. A built in timing circuit prevents false shutdown. The signal from the drain voltage is fed to the timer, providing safety for the MOSFET when in linear mode. The SC4150 latches off under abnormal condition and attempts to restart after a time out period.

The <u>device</u> comes in two options, PWRGD (SC4150H) and  $\overline{PWRGD}$  (SC4150L). These signals can be directly used to enable power modules.

### **Features**

- Programmable slew of the inrush current when used for hot insertion in the negative 24V and 48V backplane

- Closed loop operation limits the maximum current even in short circuit condition

- ◆ Built in timer prevents false shutdown, when the closed loop operation limits the current.

- Sensing the drain voltage allows for immediate shutdown in short circuit condition, where current spikes and noise is ignored.

- Power good signal

- Input UVLO and OVLO sensing

- SO-8 package

#### **Applications**

- Central office switching

- ◆ -48V Distributed power systems

- Power supply hotswap & inrush control

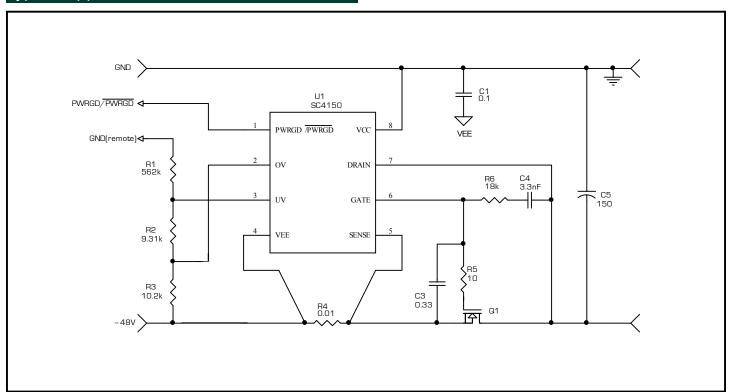

### Typical Application Circuit

Figure 1

# Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied.

| Parameter                              | Symbol                | Maximum     | Units |  |

|----------------------------------------|-----------------------|-------------|-------|--|

| Supply Voltage                         | V <sub>cc</sub>       | -0.3 to 100 | V     |  |

| DRAIN, PWRGD/ PWRGD                    |                       | -0.3 to 100 | V     |  |

| SENSE, GATE                            |                       | -0.3 to 20  | V     |  |

| UV, OV                                 |                       | -0.3 to 60  | V     |  |

| Thermal Resistance Junction to Ambient | $\theta_{JA}$         | 163         | °C    |  |

| Thermal Resistance Junction to Case    | $\theta_{	extsf{JC}}$ | 38.8        | °C    |  |

| Operating Junction Temperature Range   | T <sub>J</sub>        | -40 to 125  | °C    |  |

| Storage Temperature Range              | T <sub>STG</sub>      | -65 to 150  | °C    |  |

| Lead Temperature (Soldering) 10 sec    | T <sub>LEAD</sub>     | 300         | °C    |  |

# Electrical Characteristics

Unless specified:  $T_A$  = 25°C,  $V_{CC}$  = 48V,  $V_{EE}$  = 0V. Values in **bold** apply over full operating temperature range.

| Parameter                     | Symbol            | Test Conditions                                          | Min   | Тур   | Max   | Units |

|-------------------------------|-------------------|----------------------------------------------------------|-------|-------|-------|-------|

| DC Characteristics            |                   |                                                          |       |       |       |       |

| Supply Operating Range        | V <sub>cc</sub>   |                                                          | 10    |       | 80    | V     |

| Supply Current                | I <sub>cc</sub>   | UV = 3V, 0V = V <sub>EE</sub> , SENSE = V <sub>EE</sub>  |       | 4     | 7     | mA    |

| Circuit Breaker Trip Voltage  | V <sub>CB</sub>   | $V_{CB} = (V_{SENSE} - V_{EE})$                          | 50    | 60    | 70    | mV    |

| Gate Pin Pull-up Current      | I <sub>PU</sub>   | Gate drive ON, $V_{GATE} = V_{EE}$                       |       | -50   |       | μA    |

| Gate Pin Pull-down Current    | I <sub>PD</sub>   | Any fault condition                                      |       | 40    |       | mA    |

| Sense Pin Current             | SENSE             | V <sub>SENSE</sub> = 50mV                                |       | -0.05 |       | μA    |

| External Gate Drive           | $\Delta V_{GATE}$ | $(V_{GATE}^{}$ $-V_{EE}^{})$ , $20V < V_{DD}^{} \le 80V$ | 9     | 13    | 16    | ٧     |

|                               |                   | $(V_{GATE} - V_{EE}), 10V \le V_{DD} \le 20V$            |       | 8     |       |       |

| UV Pin High Threshold Voltage | V <sub>UVH</sub>  | UV Low to High transition                                | 1.241 | 1.273 | 1.305 | ٧     |

| UV Pin Low Threshold Voltage  | V <sub>UVL</sub>  | UV High to Low transition                                | 1.192 | 1.223 | 1.253 | V     |

| UV Pin Hystersis              | V <sub>UVHY</sub> |                                                          |       | 50    |       | mV    |

| UV Pin Input Current          | I <sub>INUV</sub> | $V_{UV} = V_{EE}$                                        |       | -0.1  |       | μA    |

| OV Pin High Threshold Voltage | V <sub>OVH</sub>  | OV Low to High transition                                | 1.192 | 1.223 | 1.253 | V     |

| OV Pin Low Threshold Voltage  | V <sub>OVL</sub>  | OV High to Low transition                                | 1.153 | 1.188 | 1.223 | V     |

| OV Pin Hystersis              | V <sub>OVHY</sub> |                                                          |       | 35    |       | mV    |

| OV Pin Input Current          | I <sub>INOV</sub> | V <sub>ov</sub> ≥ 1.5V                                   |       | -0.05 |       | μA    |

### Electrical Characteristics (Cont.)

Unless specified:  $T_A = 25^{\circ}C$ ,  $V_{CC} = 48V$ ,  $V_{EE} = 0V$ . Values in **bold** apply over full operating temperature range.

| Parameter                                                        | Symbol                | Test Conditions                                                              | Min | Тур  | Max | Units |

|------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------|-----|------|-----|-------|

| Power Good Threshold                                             | V <sub>PG</sub>       | $V_{DRAIN}$ - $V_{EE}$ , High to Low transition                              | 1.5 | 1.75 | 2.0 | V     |

| Power Good Threshold Hysteresis                                  | V <sub>PGHY</sub>     |                                                                              |     | 0.4  |     | V     |

| Drain Input Bias Current                                         | I <sub>DRAIN</sub>    | $V_{DRAIN} = 48V$                                                            |     | 15   | 50  | μA    |

| Output Low Voltage                                               | V <sub>OL</sub>       | SC4150H, $V_{OL}$ = PWRGD - $V_{DRAIN}$<br>@ $V_{DRAIN}$ = 5V, $I_{O}$ = 1mA |     | 1    |     | V     |

|                                                                  |                       | SC4150L, $V_{OL} = PWRGD - V_{EE}$<br>@ $V_{DRAIN} = 1V$ , $I_{O} = 1mA$     |     | 1    |     | V     |

| Output Leakage                                                   | I <sub>OH</sub>       | SC4150H, $V_{DRAIN} - V_{EE} = 1V$ , $V_{PWRGD} = 80V$                       |     | 1.0  | 10  | μΑ    |

|                                                                  |                       | SC4150L, V <sub>DRAIN</sub> -V <sub>EE</sub> = 5V                            |     | 1.0  | 10  | μA    |

| AC Characteristics                                               |                       |                                                                              |     |      |     |       |

| OV High to Gate Low                                              | t <sub>PHLOV</sub>    |                                                                              |     | 1.7  |     | μs    |

| UV Low to Gate Low                                               | t <sub>PHLUV</sub>    |                                                                              |     | 1.5  |     | μs    |

| OV Low to Gate High                                              | t <sub>PLHOV</sub>    |                                                                              |     | 5.5  |     | μs    |

| UV Low to Gate High                                              | t <sub>PLHUV</sub>    |                                                                              |     | 6.5  |     | μs    |

| SENSE High to Gate Low                                           | t <sub>PHLSENSE</sub> |                                                                              |     | 3    |     | μs    |

| DRAIN Low to PWRGD Low<br>DRAIN Low to (PWRGD - DRAIN)<br>High   | t <sub>PHLPG</sub>    |                                                                              |     | 0.5  |     | μs    |

| DRAIN High to PWRGD High<br>DRAIN High to (PWRGD - DRAIN)<br>Low | t <sub>PLHPG</sub>    |                                                                              |     | 0.5  |     | μs    |

| Gate ON Time - Time Delay                                        | t <sub>ON_1</sub>     | V <sub>DRAIN</sub> > 8V, after short circuit                                 |     | 5    |     | μs    |

| Gate ON Time - Time Delay                                        | t <sub>ON_2</sub>     | V <sub>DRAIN</sub> < 7V, after short circuit                                 |     | 250  |     | μs    |

| Gate OFF Time                                                    | t <sub>OFF</sub>      | SC4150, After short, prior to retry                                          |     | 100  |     | ms    |

|                                                                  |                       | SC4150-4, After short, prior to retry                                        |     | 400  |     |       |

#### Note:

(1) This device is ESD sensitive. Use of standard ESD handling precaution is required.

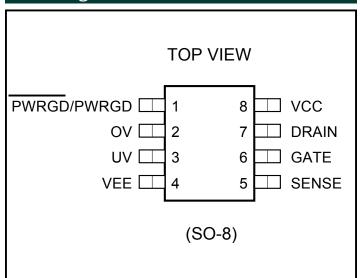

# Pin Configuration

# Ordering Information

| Part Number <sup>(1)(2)(3)</sup> | Package |

|----------------------------------|---------|

| SC4150HISTRT                     | 00.0    |

| SC4150LISTRT                     | SO-8    |

| SC4150HIS-4TRT                   |         |

| SC4150LIS-4TRT                   |         |

#### **Notes:**

- (1) Only available in tape and reel packaging. A reel contains 2500 devices.

- (2) Device marking: SC4150H, SC4150L - 100ms 4150H-4, 4150L-4 - 400ms

- (3) Lead free product.

# Pin Descriptions

| Pin | Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PWRGD/PWRGD | Power Good output pin. This pin will toggle when V <sub>DRAIN</sub> is within V <sub>PG</sub> of V <sub>EE</sub> . This pin can be connected directly to the enable pin of a power module, 0.1µF to VEE is optional.                                                                                                                                                                                                                                                                                                                            |

| 2   | OV          | Analog Overvoltage input. When OV is pulled above 1.223V threshold, an overvoltage condition is detected and the GATE pin will be immediately pulled low. The GATE pin will remain low until OV drops below the 1.188V high to low threshold.                                                                                                                                                                                                                                                                                                   |

| 3   | UV          | Analog Undervoltage input. When UV is pulled below the 1.223V threshold, an undervoltage condition is detected and the GATE pin will be immediately pulled low. The GATE pin will remain low until UV rises above the 1.273 threshold.                                                                                                                                                                                                                                                                                                          |

| 4   | VEE         | Negative supply voltage input. Connect to the lower potential of the power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5   | SENSE       | Circuit breaker sense pin. With a sense resistor placed in the supply path between $V_{\text{EE}}$ and SENSE, the circuit breaker will trip when the voltage across the resistor exceeds 60mV. Noise spikes of less than $2\mu s$ are filtered out and will not trip the circuit breaker. If the circuit breaker trip current is set to twice the normal operating current, only $25\text{mV}$ is dropped across the sense resistor during normal operation. To disable the circuit breaker, $V_{\text{EE}}$ and SENSE can be shorted together. |

| 6   | GATE        | Gate drive output for external n-channel. The GATE pin will go high when the following start-up conditions are met: the UV pin is high, t he OV pin is low and $(V_{SENSE} - V_{EE}) < 60 \text{mV}$ . The GATE pin is pulled high by a 50µA current source and pulled low with a 40mA current source.                                                                                                                                                                                                                                          |

| 7   | DRAIN       | Analog Drain sense input. Connect this pin to the drain of the external N- $\underline{\text{channel}}$ FET and the V(-) pin of the power module. When the DRAIN pin is below $V_{PG}$ , the PWRGD or PWRGD pin will toggle.                                                                                                                                                                                                                                                                                                                    |

| 8   | VCC         | Positive supply voltage input. Connect this pin to the higher potential of the power supply input and the V(+) pin of the power module.                                                                                                                                                                                                                                                                                                                                                                                                         |

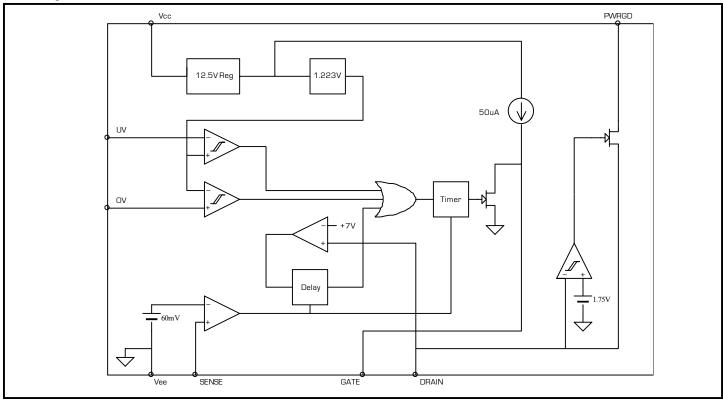

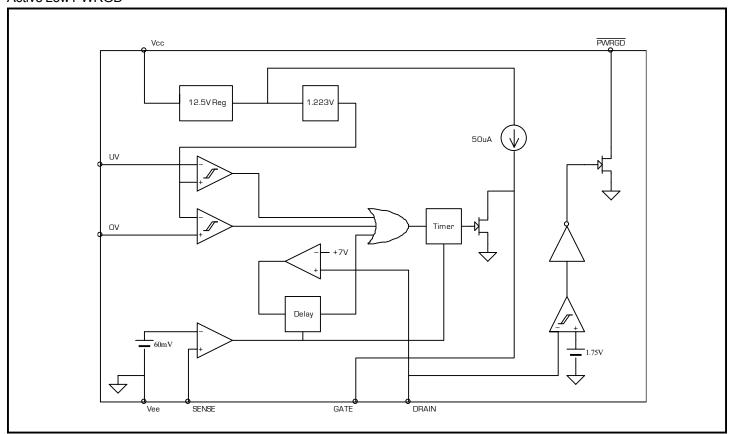

# Block Diagram

# Active High PWRGD

# Active Low PWRGD

#### Applications Information

Insertion of a power circuit board into a live backplane would draw enormous inrush currents. This is mostly due to the charging of the bulk electrolytic capacitors at the input of the power module being plugged in.

The transient currents would send glitches all over the power system and could cause corruption of the signals and even a power down if the source isn't able to handle these high surges.

This section describes the components selection needed for a typical application utilizing the SC4150. Let's assume the following requirements for a representative system:

Input voltage range: 36V to 72V

Nominal current: 2A typ.

Over-current condition: 5A

Bulk capacitance: Cload = 150µF

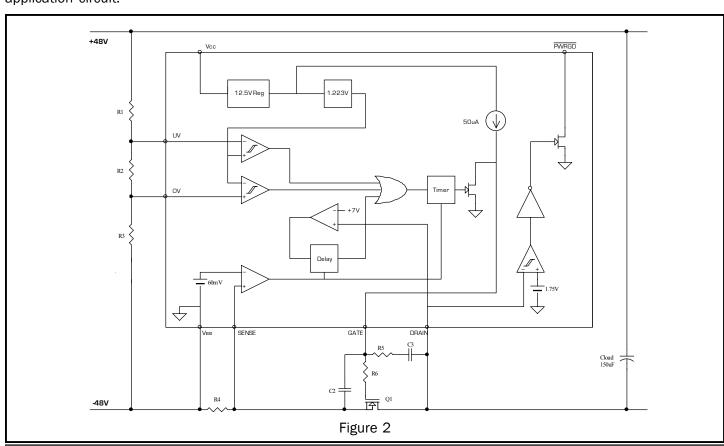

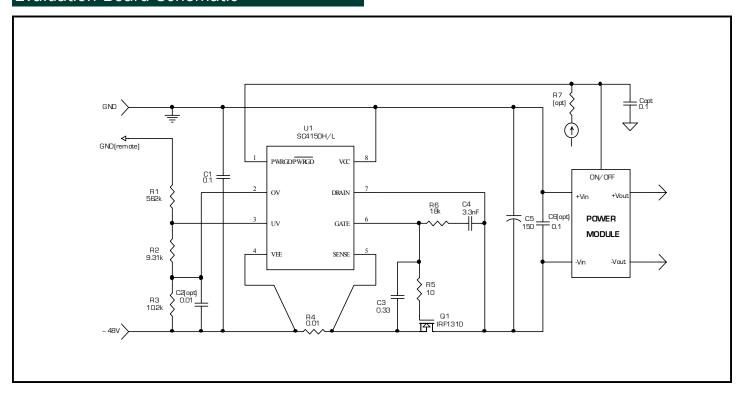

The schematic in Figure 2 combines internal function blocks along with the external components of the application circuit.

**Resistors R1, R2 and R3** make up a voltage divider to set the Under-Voltage (UV) and Over-Voltage (OV) trip points.

When the input power supply ramps up the UV trips at 1.273V and OV trips at 1.223V; during the ramp down transition the UV trips at 1.223V and OV trips at 1.198V.

The 50mV hysteresis for UV and 25mV hysteresis for OV provide the necessary guard-bands to prevent false tripping during power up and power down conditions.

As an additional noise killing and stabilizing measure, the **capacitor C1** should be placed at the OV terminal with the value in range from 1,000 to 10,000pF.

For the UV=38V and OV=70V the values of the resistor can be calculated as follows:

$$Vuv = 1.273V \cdot (R1+R2+R3) \div (R2+R3)$$

$$Vov = 1.223V \cdot (R1+R2+R3) \div R3$$

## Applications Information (Cont.)

With the input bias current of the UV and OV comparators in the range of 20-30nA, let's choose the R1 to be  $562k\Omega$ . This yields the values of R2=9.31k $\Omega$  and R3 =

$10.2k\Omega$ . With these values the accuracy is about 1% which is quite acceptable for those functions.

**Resistor R4** sets the over-current trip. To choose R4, the user must determine the level of the current where it should trip. As a rule of thumb, the over-current is set to be 200-300% of the nominal value. In our case, we assumed this value to be 5A.

Considering the minimum trip voltage is 50mV the value of R4 is 50mV  $\div$  5A = 10 m $\Omega$ .

The tolerance of this resistor is usually price driven and 5% is an adequate range of accuracy.

The actual position and layout of the circuitry around the sense resistor R4 is critical to avoid a false over-current tripping. The trace routing between R4 and SC4150 should be as short as possible and wide enough to handle the maximum current with zero current in the sense lines – ideally "Kelvin" like.

Additionally, there is a short delay circuit at the comparator to filter out unwanted noise and otherwise induced transients.

**Inrush Current** is being controlled by the **R5C3** network and swamping capacitor **C2**.

When a board is plugged into a live backplane, the input bulk capacitance of the board's power supply produces large current transients due to the rush of the currents charging those capacitors. The main feature of the SC4150 is to provide an orderly and well-controlled inrush current.

Since the minimum trip voltage is 50mV, let's choose the inrush current to be 3A.

$Imax = Cload \cdot \Delta Vmax / dt$

dt = Cload ·  $\Delta$ Vmax /Imax = 150 $\mu$ F · 70V / 3A = 3.5ms

This would be the minimum time for the gate voltage plateau during which the Vdd linearly decreases maintaining 3A charge current of the Cload.

The inrush can be calculated using the following equation:  $I_{MAX} = (50 \mu A \cdot C_{IOAD}) / C3$

With the values shown in the schematic the actual inruch current will be about 2A, which is within the limits we have chosen.

Resistor **R5** will produce a time constant which prevents Q1 from turning on when power is initially applied and the circuit is not ready to actively pull the gate low. It's value is not critical and 18k ensures the adequate delay.

The value of **C2** is chosen to prevent false turn-on of the FET due to the current flowing via C3 into the gate of the FET when the circuit initially connects to the power source. Capacitors C2 and C3 form a divider from Vin to GND. C2 must keep the initial voltage at the gate below Vth minimum.

For the typical FET, this threshold is around 1V to 2V, therefore C2 = 100 • C3 will keep gate voltage at 0.7V, even at the "worst" case of Vin = 70V.

The choice of the **Q1** is quite straightforward and is guided mostly by thermal considerations due to the power dissipation in the steady state.

For instance, in our case, the nominal current is 2A, the power dissipation due to the conducting losses will be

Pdis =  $Inom^2 \cdot Rds_on.$

The MOSFET should be able to withstand Vdss  $\geq 100V$  with continuous drain current Id  $\geq 6A$ . Device SUD06N10 or similar fits this application. It has an Rds\_on =  $0.2\Omega$ , and will dissipate

Pdis =  $2^2 \cdot 0.2 = 0.8W$ , which can be handled by this DPAK device.

If there is a consideration of reducing the temperature of the MOSFET then the lower Rds\_on device should be chosen or a different style (D2PAK) which has lower Junction-to-Ambient thermal characteristics.

The **R6** has a function of dumping high frequency oscillations. The value of it is not critical and can be in the range of  $5\Omega$  to  $20\Omega$ .

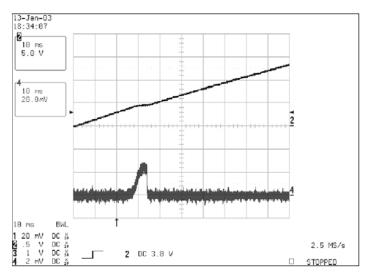

### Typical Characteristics

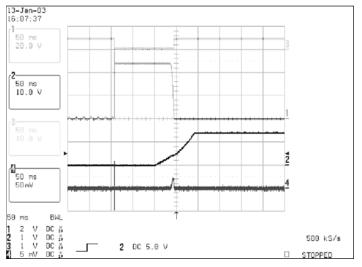

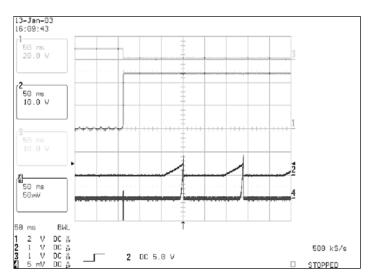

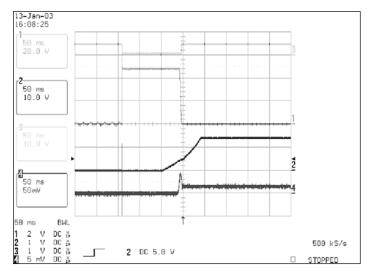

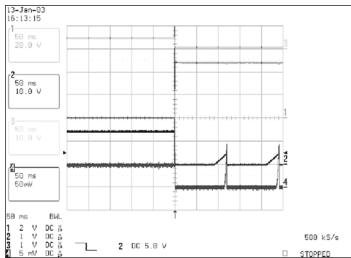

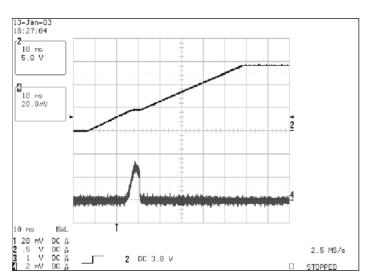

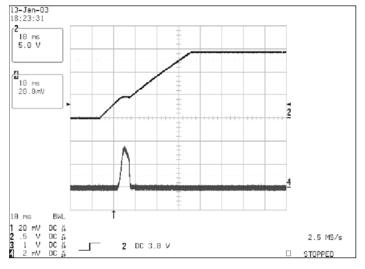

Below are the snap-shots taken at start-up with different loading conditions and during the application of the overcurrent at the output of the circuit.

For all figures, Ch1:  $V_{DRAIN}$ ; Ch2:  $V_{GATE}$ ; Ch3: PWRGD; Ch4:  $V_{R4}$  (Input current)

Figure 3. Start-up with no load.

Figure 4. Start-up in over load.

Figure 5. Start-up with 1Amp load.

Figure 6. From 3A load into "short circuit".

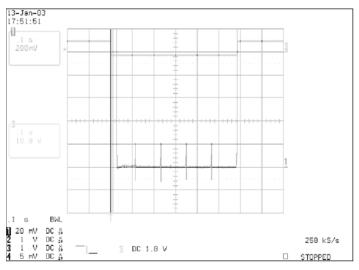

### Typical Characteristics (Cont.)

The following set of snapshots demonstrates effectiveness of SC4250 circuit in the case where connection to the live back plane is very "bouncy", which is usually the situation with manual replacements of the power cards.

For all figures, Ch1:  $V_{DRAIN}$ ; Ch2:  $V_{GATE}$ ; Ch3: PWRGD (referenced to  $V_{DRAIN}$ ); Ch4:  $V_{R4}$  (Input current)

Figure 7. Short circuit hiccup.

Figure 8. Inrush limit.

Figure 9. Inrush limit.

Figure 10. Inrush limit.

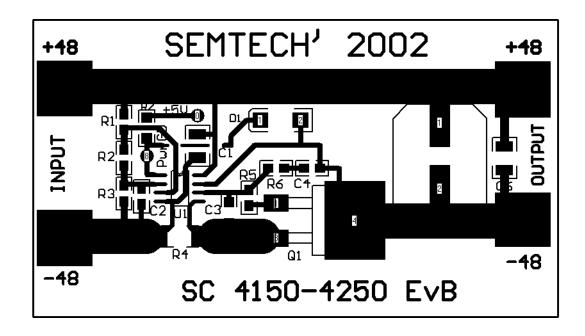

# **Evaluation Board Schematic**

## **Evaluation Board**

# Evaluation Board - Bill of Materials

| Ref | Qty | Designator | Value       | Description  | Footprint |

|-----|-----|------------|-------------|--------------|-----------|

| 1   | 1   | C1         | 0.1/100V    | Ceramic cap  | 1210      |

| 2   | 1   | C2 (opt.)  | 0.01        | Ceramic cap  | 0805      |

| 3   | 1   | C3         | 0.33        | Ceramic cap  | 1206S     |

| 4   | 1   | C4         | 0.0033/100V | Ceramic cap  | 0805      |

| 5   | 1   | C5         | 150/80V     | Aluminum cap | CAP-AL-H  |

| 6   | 1   | C6 (opt.)  | 0.1/100V    | Ceramic cap  | 1210      |

| 7   | 1   | Q1         | IRF1310     | MOSFET       | D2PAK     |

| 8   | 1   | R1         | 562k        | Resistor     | 0805      |

| 9   | 1   | R2         | 9.31k       | Resistor     | 0805      |

| 10  | 1   | R3         | 10.2k       | Resistor     | 0805      |

| 11  | 1   | R4         | 0.01        | Resistor     | 2010CS    |

| 12  | 1   | R5         | 10          | Resistor     | 0805      |

| 13  | 1   | R6         | 18k         | Resistor     | 0805      |

| 14  | 1   | R7         | 5.1k        | Resistor     | 1206S     |

| 15  | 1   | U1         | SC4150      | Semtech IC   | SO-8      |

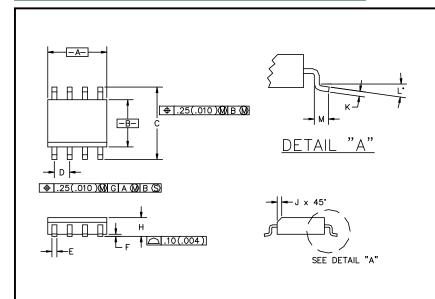

## Outline Drawing - SO-8

| DIMENSIONS |      |      |      |      |      |  |  |

|------------|------|------|------|------|------|--|--|

| DIMN       | INC  | HES  | М    | NOTE |      |  |  |

| ייואווט    | MIN  | MAX  | MIN  | MAX  | NOIL |  |  |

| Α          | .188 | .197 | 4.80 | 5.00 |      |  |  |

| В          | .149 | .158 | 3.80 | 4.00 |      |  |  |

| С          | .228 | .244 | 5.80 | 6.20 |      |  |  |

| D          | .050 | BSC  | 1.27 | BSC  |      |  |  |

| Ε          | .013 | .020 | 0.33 | 0.51 |      |  |  |

| F          | .004 | .010 | 0.10 | 0.25 |      |  |  |

| Н          | .053 | .069 | 1.35 | 1.75 |      |  |  |

| J          | .011 | .019 | 0.28 | 0.48 |      |  |  |

| K          | .007 | .010 | .19  | .25  |      |  |  |

| L          | 0,   | 8°   | 0°   | 8°   |      |  |  |

| М          | 016  | 050  | 0.40 | 1 27 |      |  |  |

JEDEC REF: MS-012AA

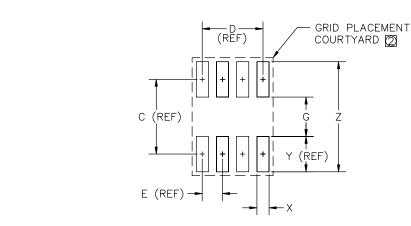

## Minimum Land Pattern - SO-8

|         | DIMENSIONS (1) |     |      |      |      |  |  |  |

|---------|----------------|-----|------|------|------|--|--|--|

| DIMN    | INCHES         |     | M    | NOTE |      |  |  |  |

| ייואווט | MIN            | MAX | MIN  | MAX  | NOIL |  |  |  |

| С       | _              | .19 | -    | 5.00 | _    |  |  |  |

| D       | _              | .15 | _    | 3.81 | _    |  |  |  |

| Ε       | _              | .05 | _    | 1.27 | _    |  |  |  |

| G       | .10            | .11 | 2.60 | 2.80 | _    |  |  |  |

| Χ       | .02            | .03 | .60  | .80  | _    |  |  |  |

| Υ       | _              | .09 | _    | 2.40 | _    |  |  |  |

| Z       | _              | .29 | 7.20 | 7.40 | _    |  |  |  |

- ② GRID PLACEMENT COURTYARD IS 12×16 ELEMENTS (6 mm X 8mm) IN ACCORDANCE WITH THE INTERNATIONAL GRID DETAILED IN IEC PUBLICATION 97.

- CONTROLLING DIMENSION: MILLIMETERS

## Contact Information

Semtech Corporation

Power Management Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805)498-2111 FAX (805)498-3804